1. Draw the pin diagram of 8288.

The pin diagram of the 8288 bus controller is shown in Fig. 5.38. The functions of the pins are described in this section.

S̅2, S̅1, S̅0 (Status Input Signals) These arc bus cycle status signals. These are decoded and control signals are generated.

CLK This is an input signal. It is connected to CLK output of the clock generator 8284.

A̅E̅N̅, CEN, IOB These are bus priority and mode control signals. A̅E̅N̅ (bus priority control/enable), CEN(Command Enable) and IOB (mode control) signals are used to generate various control signals.

M̅R̅D̅C̅ (Memory Read Control Signals) These command signals are used to load the content of memory location on the data bus.

M̅W̅T̅C̅ (Memory Write Control Signals) These command signals are used to store the available data on the data bus to the specified memory location.

I̅O̅R̅C̅ (I/O Read Control Signals) The I/O device is able to put the available data of the addressed port on the data bus.

I̅O̅W̅C̅ (I/O Write Control Signals) The I/O device is able to accept the available data port on the data bus and send to the addressed port.

A̅M̅W̅C̅ (Advance Memory Write Control Signal) This signal is activated one clock period earlier than M̅W̅T̅C̅.

A̅I̅O̅W̅C̅ This signal is activated one clock period earlier than I̅O̅W̅C̅.

MCE/P̅D̅E̅N̅ Cascade/Peripheral data Enable. This signal is used in Priority Interrupt Controller 8259A.

I̅N̅T̅A̅ (Interrupt Acknowledge) This is used as output signal during two interrupt acknowledge bus cycles and is used as memory read control signal.

ALE Address Latch Enable signal.

DT/R̅ Data Direction Control signal.

DEN Data buffer control signal.

VCC Power Supply Input + 5 V.

GND (Ground) This pin is connected system ground.

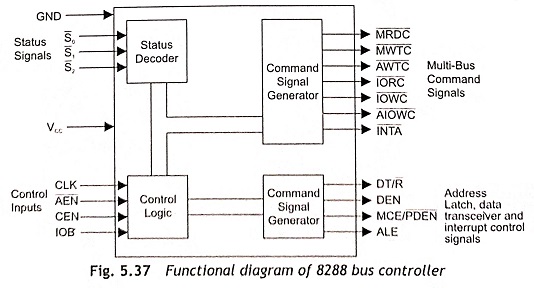

2. Draw the functional block diagram of 8288.

Ans. The functional block diagram of 8288 is shown in Fig. 19a.2.

3. Is 8288 always used with 8086?

Ans. No, the bus controller IC 8288 is used with 8086 when the latter is used in MAX mode.

4. What are the inputs to 8288?

Ans. There are two sets of inputs—the first set is the status inputs S0 , S1 and S2 . The second set is the control inputs having the following signals: CLK, AEN, CEN and IOB.

5. What are the output signals from 8288?

Ans. There are two sets of output signals—Multibus command signals and the second set includes the bus control signals—Address Latch, Data Transreceiver and Interrupt Control Signals.

The multibus command Signals are the Conventional MEMR, MEMW, IOR and IOW signals which have been renamed as MRDC, MWTC, IORC, IOWC, where the suffix ‘C’ stands for command. INTA signal is also included in this.

Two more signals— AMWC and AIOWC are the advanced memory and I/O write commands. These two output signals are enabled one clock cycle earlier than normal write commands. Some memory and I/O devices require this wider pulse width.

The bus control signals are DT/ R , DEN, ALE and MCE/ PDEN . The first three are identical to 8086 output signals when operated in the MIN mode—with the only difference here is that the DEN output signal of 8288 is an active high signal.

MCE/ PDEN (Master Cascade Control/Peripheral Data Enable) is an output signal having two functions—I/O bus control or system bus control. When this signal status is low, its function is identical to DEN signal and it operates in I/O mode. When high, this signal ensures the sharing of the system buses by other processors connected to the system.

In the system bus control mode, the signals AEN (address enable) and IOB both have to be low. This then permits more than one 8288 and 8086 to be interfaced to the same set of system buses. In this case, the bus arbiter IC 8289 selects the active processor by enabling only one 8288, via the AEN input. In this system bus mode MCE/ PDEN signal becomes MCE-Master Cascade Control and is used during an interrupt sequence to read the address from a master priority interrupt controller (PIC).

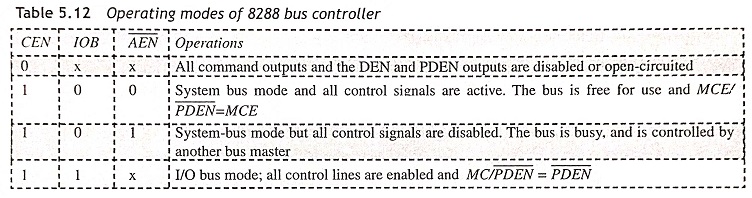

The operating modes of 8288 are determined by CEN (command enable), IOB, (I/O bus) and AEN signals and shown in Table 19a.1.

6. Discuss the status pins S2 , S1 and S0 .

Ans. These are three input pins for 8288 and come from the corresponding pins of 8086 (its output pins). The command-decode definitions for various combinations of the three signals are shown in Table 19a.2.

7. Discuss the three pins (a) IOB (b) CEN and (c) AEN of 8288.

Ans. (a) IOB stands for input/output bus mode and is an input signal for 8288. When IOB = high, 8288 functions in the I/O bus mode and when IOB = low, 8288 functions in the system bus mode.

(b) CEN stands for command enable and is an input signal for 8288. When CEN = low, all command outputs of 8288 and the DEN and the PDEN control outputs are forced into active state and not tri-stated. This feature is utilised for memory partitioning implementation. This also eliminates address conflicts between system bus devices and resident bus devices. Again, when CEN = high, these outputs are in the enabled state.

(c) AEN stands for address enable and is an input signal for 8288. This signal enables command outputs of 8288 a minimum of 110 ns (and a maximum of 250 ns) after it becomes low (i.e., active). If AEN = 1, then command output drivers are put to tri-state. In the I/O bus mode (IOB = 1) AEN signal does not affect the command lines.

Comments

Post a Comment