8255A - Programmable Peripheral Interface

8255A - Programmable

Peripheral Interface

The 8255A is a general-purpose programmable I/O device designed to transfer the data from I/O to

interrupt I/O under certain conditions as required. It can be used with almost

any microprocessor.

It consists of three

8-bit bidirectional I/O ports (24 I/O lines) which can be configured as per the

requirement.

Ports of 8255A

8255A has three ports,

i.e., PORT A, PORT B, and PORT C.

- Port A contains one 8-bit output latch/buffer and one 8-bit input buffer.

- Port B is similar to PORT A.

- Port C can be split into two parts, i.e. PORT C lower (PC0-PC3) and PORT C upper (PC7-PC4) by the control word.

These three ports are

further divided into two groups, i.e. Group A includes PORT A and upper PORT C.

Group B includes PORT B and lower PORT C. These two groups can be programmed in

three different modes, i.e. the first mode is named as mode 0, the second mode

is named as Mode 1 and the third mode is named as Mode 2.

Features of 8255 A

The prominent features

of 8255 A are as follows −

- It consists of 3 8-bit IO ports i.e. PA, PB, and PC.

- Address/data bus must be externally demux'd.

- It is TTL compatible.

- It has improved DC driving capability.

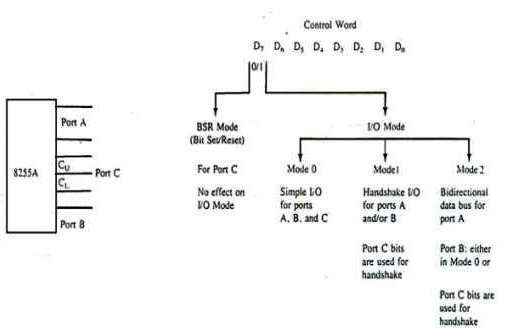

Figure A: 8255 I/O ports and their modes

The 8255 A is contained in a 40-pin package, whose pin out is shown in fig.B

Figure B:- Pin Configuration of 8225

The block diagram is shown in fig. C

Figure C:- Functional Block Diagram of Intel 82255 PPI Functional Description:

This support chip is a

general-purpose I/O component to interface peripheral equipment to the

microcomputer system bus. It is programmed by the system software so that

normally no external logic is necessary to interface peripheral devices or

structures.

Data Bus Buffer:

It is a tri-state 8-bit

buffer used to interface the chip to the system data bus. Data is transmitted

or received by the buffer upon execution of input or output instructions by the

CPU. Control words and status information are also transferred through the data

bus buffer. The data lines are connected to BDB of 𝜇p.

Read/Write and Logic

Control:

The function of this

block is to control the internal operation of the device and to control the

transfer of data and control or status words. It accepts inputs from the CPU

address and control buses and, in turn, issues command to both the control

groups.

C S (Chip Select):

A low on this input

selects the chip and enables the communication between 8255A & the CPU. It

is connected to the output of address decode circuitry to select the device

when it is addressed.

R D (Read):

A low on this input

enables the 8255A to send the data or status information to the CPU on the data

bus.

W R (Write):

A low on this input pin

enables the CPU to write data or control words into the 8255A.

Control word:

Figure D shows a

register called the control register. The control of this register, called the

control word, specify an I/O function for each port this register can be.

Figure D:8225A an I/O ports

Figure E:8255A chip select logic (a) and I/O port addresses (b)

Accessed to write a control word when A0 and A1 are at logic1 , the register is not accessible for a read operation. Bit D7 of the control register either specifies the I/O function or the bit Set/Reset function, as classified in figure 1. If bit D7=0, bits D6-D0 determine I/O function in various mode, as shown in figure 4.if bit D7=0 port C operates in the bit Set/Reset (BSR) mode. The BSR control word does not affect the function of port A and B

BSR Mode

Functional Description:

This support chip is a

general-purpose I/O component to interface peripheral equipment to the

microcomputer system bus. It is programmed by the system software so that

normally no external logic is necessary to interface peripheral devices or

structures.

Data Bus Buffer:

It is a tri-state 8-bit

buffer used to interface the chip to the system data bus. Data is transmitted

or received by the buffer upon execution of input or output instructions by the

CPU. Control words and status information are also transferred through the data

bus buffer. The data lines are connected to BDB of 𝜇p.

Read/Write and Logic

Control:

The function of this

block is to control the internal operation of the device and to control the

transfer of data and control or status words. It accepts inputs from the CPU

address and control buses and, in turn, issues command to both the control

groups.

C S (Chip Select):

A low on this input

selects the chip and enables the communication between 8255A & the CPU. It

is connected to the output of address decode circuitry to select the device

when it is addressed.

R D (Read):

A low on this input

enables the 8255A to send the data or status information to the CPU on the data

bus.

W R (Write):

A low on this input pin

enables the CPU to write data or control words into the 8255A.

Control word:

Figure D shows a

register called the control register. The control of this register, called the

control word, specify an I/O function for each port this register can be.

REFERENCES

- R. S. Gaonkar, Microprocessor Architecture, Programming, and Applications with the 8085, Fifth Edition, Penram International Publishing (India) Private Limited.

- S Ghoshal, Microprocessor Based System Design, Macmillan India Limited, 1996

- M. Mano, Digital Logic and Computer Design, Prentice – Hall India

- B. Ram - Fundamentals of Microprocessor and Microcontrollers

- “Microprocessors: Principles and Applications” by A Pal

- “Microprocessors and Microcontrollers : Architecture, Programming and Interfacing Using 8085, 8086 and 8051” by Soumitra Kumar Mandal

- “Introduction to Microprocessors and Microcontrollers” by Crisp John Crisp

- “Microprocessors And Microcontrollers” by A Nagoor Kani

- “Microprocessors And Microcontrollers : Architecture, Programming and System Design 8085, 8086, 8051, 8096” by KRISHNA KANT

- “8 - Bit Microprocessor” by Vibhute

Comments

Post a Comment